超高压 SiC 与超共源共栅

发布时间:2024-06-18 作者: 塑料外壳式断路器系列

发布时间:2024-06-18 作者: 塑料外壳式断路器系列

技术相比,该技术的系统平衡成本和运行损耗要明显降低。该技术的应用场景范围非常广,从固态变压器、中压电机驱动器到智能电网应用(FACTS、STATCOM)和高压直流断路器均包含在内。SiC MOSFET 被认为是在不久的将来颠覆这一领域的绝佳选择,UnitedSiC 提供了独特的方法来加速采用基于宽带隙的高压开关。这种方法被称为超共源共栅 (Supercascode)。我们将这种方法及其已证明的性能与

在过去的十年中,高压 SiC器件领域取得了许多进步。从理论上讲,可以开发出最大额定电压至少为硅器件10倍的 SiC 器件。沿着这些思路,许多演示展示过高达 15kV单个 SiC MOSFET,甚至是高达 27kV的 SiCIGBT。6.5kV-10kV范围内的 MOSFET正在慢慢的变成为基于模块的产品。这充分证明,在 3.3kV以上时,相对于硅 IGBT,SiC MOSFET可以明显降低损耗。

对于 10-25kV电压的 SiC IGBT,载流子寿命提高和控制、超厚外延层的增长、器件可靠性和最佳特性等挑战正在攻克中,产品仍需 5-10年才能问世。

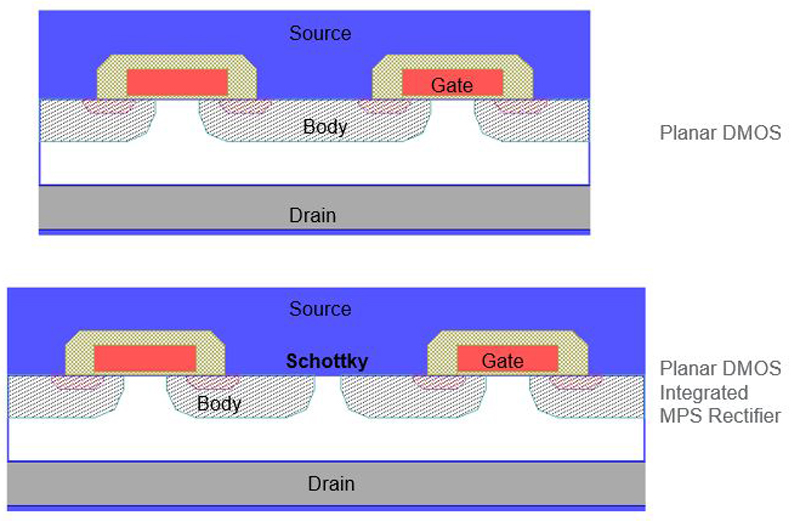

在大于 3.3kV的领域,目前使用及正在开发的主要器件结构为平面式 MOSFET和集成了合并式 P-i-N肖特基二极管(MPS) 的 MOSFET,如图 1所示。后一种器件无需在模块中添加额外的 SiC肖特基二极管,从而为 MOSFET提供了更多封装空间,并提高了可用的额定电流,因为通过增加芯片尺寸来增加每个单元内的肖特基空间的可能性不大。但是,由于目标应用需要较高的额定电流,因此就需要有源面积为 0.5-1cm2的相对较大的器件,而采用 SiC时这一些器件很难以高产量生产。

图 1:处于开发中的适合更高电压的 SiC应用的平面式 MOSFET(a)和集成肖特基的 MOSFET (b)的结构。需要将许多这样的器件在模块中并联才可以做到所需的额定电流,并且每个芯片都会开关整个总线电压

高压器件面临的一个关键挑战是,较厚的外延层会导致启动外延晶片时出现更多缺陷。这些较厚且掺杂较少的层具有更多的掺杂变化,因为随着掺杂水平达到1014cm-3的水平,就很难维持严格的掺杂控制。随着厚度的增加,外延期间的耗材成本也更高。当前最先进的技术能让最高 3.3kV的器件获得高质量的30um外延层,并且在未来几年内 6.5kV-10kV(50-90um)的层将得到增强并达到可以投产的质量。额定值为 1.7kV及以下的外延层在 6英寸 4H-SiC衬底上可获得非常高质量和紧密的参数分布。

封装超高压开关时会出现许多有趣的挑战。当单个开关通过 5kV总线ns内关闭时,我们得到的 dV/dt 值为200V/ns。10pF的杂散电容(例如,从芯片漏级到基板的或跨栅极电路隔离栅的杂散电容)将导致每个芯片有 2A(C*dV/dt)的位移电流。由于大功率模块往往具有许多(10-20个)并联芯片,此问题可能变得很严重。这些杂散电流会导致额外的损耗,并且还会导致低压栅极驱动电子器件出现严重的误触发问题。位移电流过大也会同时削弱模块内部以及外部电缆和电路中的绝缘措施。

在额定 10kV的器件中,在器件末端顶部的 1mm区域中会产生 10kV的压降。这就需要在模块制造期间非常仔细地注意器件的封装和清洁度,以避免气穴、局部放电,以及母线和键合线在该区域附近产生的任何破坏性电势。还需要厚陶瓷来将开关与基板隔离,而这会导致热阻增加。例如,将单个直接覆铜陶瓷基板 (DBC)用于 15kV器件将需要 AlN层厚度超过 1mm。陶瓷基板上迹线的场分布必须得到良好管理,以控制局部放电以及从模块中的芯片到基板的最终灾难性短路。

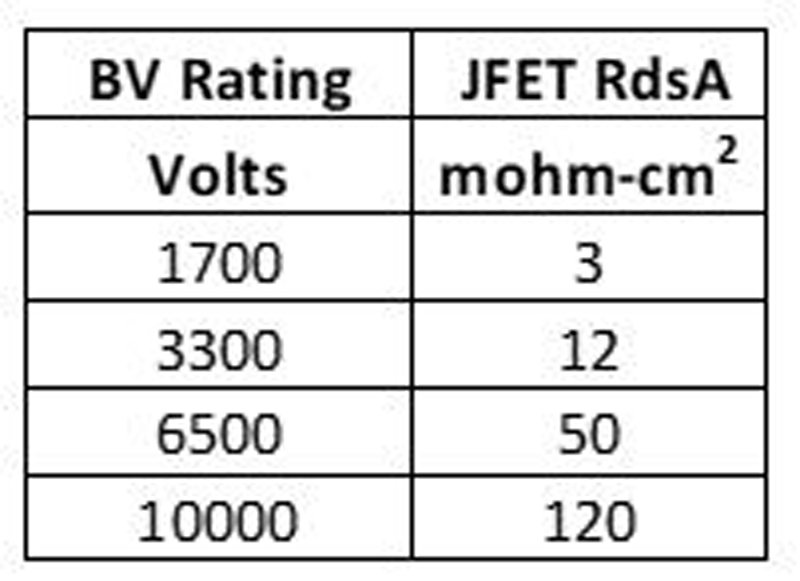

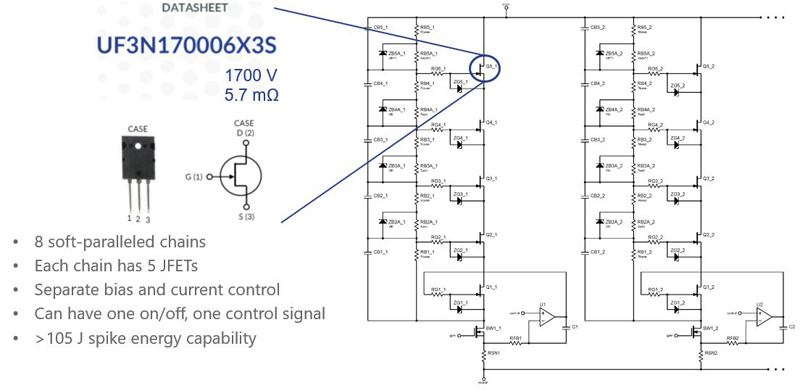

UnitedSiC开发了一种独特的方法,使用超共源共栅的概念来制造高压 SiC器件,该方法基于多个低电压器件的串联连接,并通过单个栅极驱动器做相关操作。让我们来研究一下这种方法背后的基本逻辑。表 1显示了 1cm2SiCJFET 的电阻与额定击穿电压的关系。考虑以并联 6500V器件来构建 6500V、12.5mohm模块的示例。那将需要 4个面积为 1cm2的芯片,每个芯片之间并联。或者,我们大家可以通过串联放置 4个 1cm23mohm、1700V的芯片(3 x 4 = 12mohm)来获得相同的电阻。因此,串联解决方案实质上使用了相同数量的 SiC晶体管,但是较低压器件的成本明显较低,并且易于制造,具有更高的良率和更好的参数分布。

表 1:1700V至 30kV下 SiC JFET的比导通电阻。请注意,4个串联的 1cm2芯片与 4个并联的 6.5kV芯片具有相同的电阻。这就是超共源共栅方法的基本逻辑

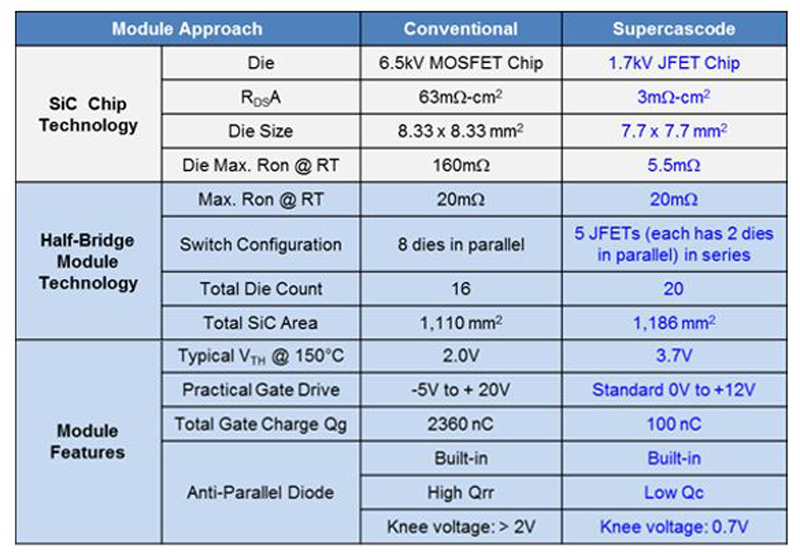

尽管可以将相同的概念用于 SiC MOSFET,但每个低压模块都要自己的同步栅极驱动。这样就增加了复杂性。使用超共源共栅方法,串联链底部的单个低压 MOSFET可控制整个串联开关。这样,超共源共栅方法的栅极电荷要求变得比需要驱动并联高压 MOSFET甚至串联高压 MOSFET模块的方法低很多。表 2比较了超共源共栅模块与通过并联 SiC MOSFET制成的等效模块的预期特性。

表 2:超共源共栅模块与通过将 SiC MOSFET和集成肖特基二极管并联而制成的模块之间的比较。请注意栅极电荷的差异

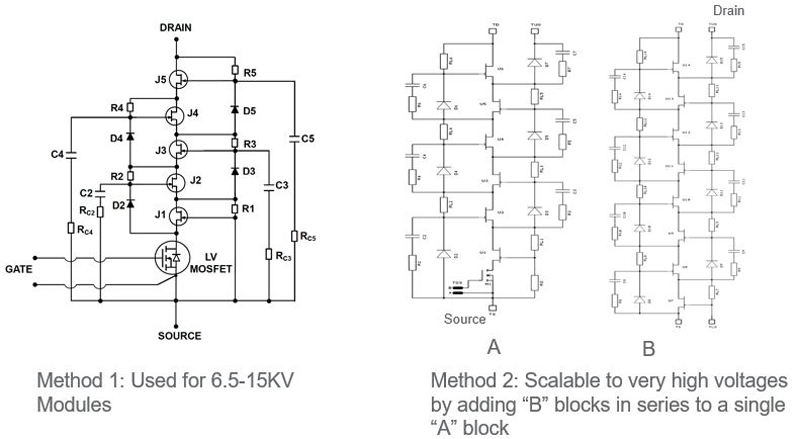

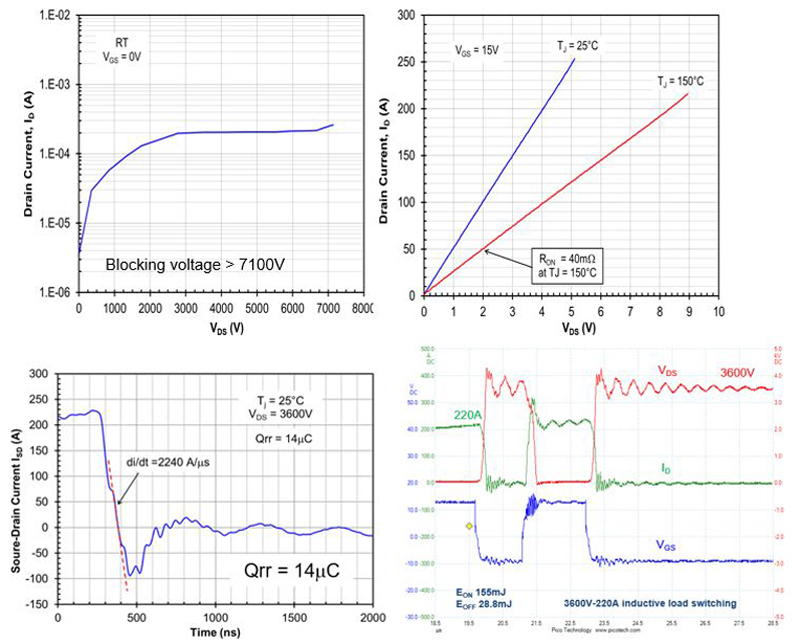

人们为超共源共栅设计了许多实现方案,图 2展示了由 UnitedSiC开发的两种电路。该模块需要一个无源平衡网络,该网络嵌入在模块内部,如图 3所示。由于热耗散主要由 SiC JFET决定,因此将它们放置在直接覆铜基板 (DBC)上以进行相对有效的散热。其他网络组件位于该层上方的电路板层中。图 4展示了 UnitedSiC正在开发的该超共源共栅模块的电气特性。该器件可阻断所需的电压,导通电阻为 20mohm (25℃),并且不需要 SiC JBS 二极管,因为第三象限拐点电压仅为 0.7V,来自硅 MOSFET,随后是电阻为 19mohm的串联 JFET。二极管恢复电荷 QRR非常低 (14uC),并且与温度无关。半桥开关波形表明,在 3600V、220A下开关时,EON(155mJ) 和 EOFF(28.8mJ) 非常低。

图 2:实现由 UnitedSiC开发的超共源共栅结构的两种电路方法。每一级具有相等数量电容器的第二种电路 (b) 已用于高达 40kV的开关中

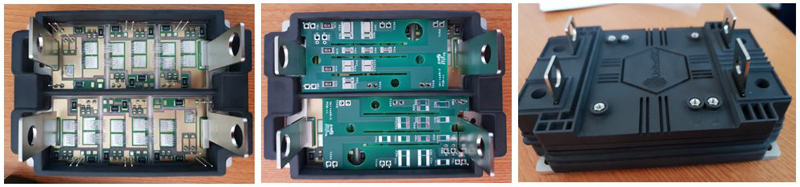

图 3:正在开发的 200A、6500V超共源共栅模块的内部结构。功率大部分消耗在 DBC表面上的 SiC JFET中。平衡网络位于电路板位置,因为其不会消耗太多功率

图 4:200A、6500V模块原型的电气特性。半桥模块有很低的导电和开关损耗。超共源共栅的恢复特性导致 QRR非常低

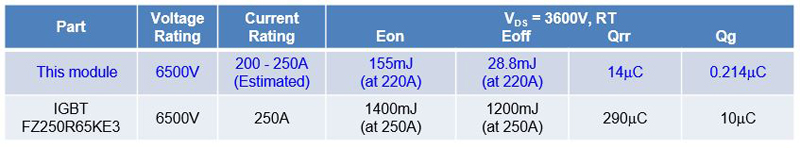

如表 3所示,功率损耗大大低于 IGBT。在随后的段落中,我们将研究这些低损耗在一系列应用中可能会产生的影响。

表 3:超共源共栅模块的损耗与相似额定值的 IGBT的损耗之间的比较。鉴于超共源共栅模块的开关损耗较低,因此明显可以在 10倍高的频率下使用

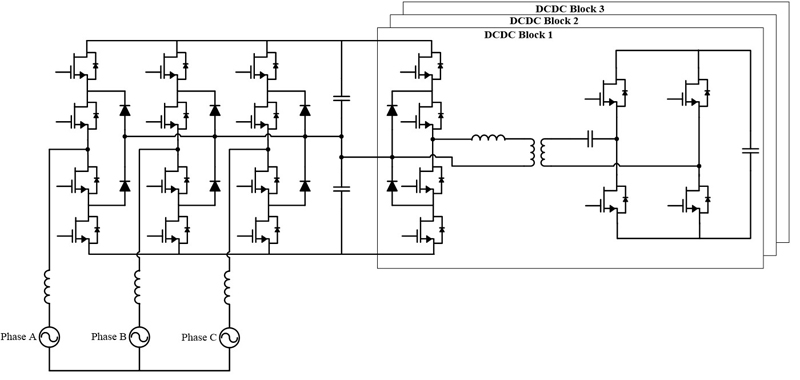

固态变压器一般会用中压或高压交流输入,例如 4160V交流电,13.8kV交流电,并将其转换为较低的电压输出,而无需使用笨重的 60Hz 变压器。基本概念如图 5所示,它先对交流电压进行整流,然后再转换为 5-100kHz 范围内的大功率、高频交流电。小得多的中高频变压器可提供较低的副边电压,可以对其进行整流以提供低压直流母线。然后,该电压可用于为电动车充电或驱动直流-交流逆变器,以管理较低电压的电机负荷。固态变压器的尺寸通常比 60Hz 变压器小很多,从而允许在非常高的电压下进行功率分配,并在使用时转换为较低的电压。这样就减少了分配功率的电流,减少了铜的重量和成本,并减少了损耗。这对于兆瓦级的功率尤其有用,例如在直流快速充电站中需要以 250-350KW 为 8-10辆车充电,或者用在大型船舶上,以减少在分配较低交流电压时发生的铜损。

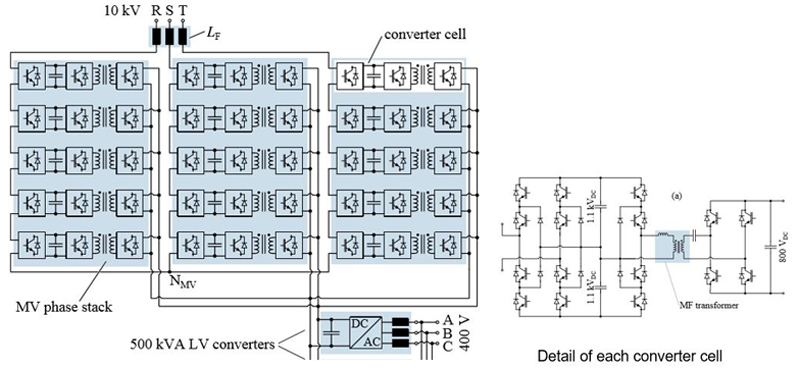

原边侧整流电压大于 6kV,若需要高于 500Hz -1kHz 的开关频率,则不可以使用 3.3kV-6.5kV级的 IGBT或IGCT。取而代之的是,用户都能够选择使用具有 7个以上电平的 1700VIGBT的多电平逆变器体系结构,或者是模块化多电平转换器 (MMC),它具有许多级联的低电压转换器,定时提供阶跃正弦输出。模块化多电平转换器的实例如图 6所示,其中转换器的每一级在原边侧都使用三电平 1700VIGBT模块。图 7展示了具有 10kV开关的三电平 SiC器件的实现。显然,SiC器件的实现大大简化了此类直流-交流转换器的架构和控制,并且可以在相对较高的频率下运行。

图 6:基于硅的模块化多电平转换器系统的实现,以实现固态变压器(作者:苏黎世联邦理工学院 Huber等人)。每个级联转换器单元中的原边均具有三电平 1700V模块。然后,需要控制所有这些开关和所有这些转换器以提供所需的输出正弦波形

图 7:使用高压 SiC MOSFET或超共源共栅来实现要简单得多。控制复杂性大大降低,且高压器件的数量大大减少。为了使用小型变压器,开关频率现在必须是硅解决方案的 10倍,并且损耗仍必须保持可控水平,以免使热管理复杂化。这正是高压 SiC器件的优势所在

美国能源部对美国的用电情况进行的调查显示,兆瓦级工业电机驱动消耗的电量占所有发电量的 14%。通过将这些电机与变速驱动器一起使用,而不是直接接入电网,可以大大节省运营成本。这些电机驱动器必须在较高的总线电压下运行,以减少工作电流来控制导线尺寸和损耗,基于硅的逆变器的工作频率为 500Hz -2kHz,取代它的基于 SiC的逆变器可以用于 10倍于此的频率,大大减少了冷却需求并减小了系统尺寸。

系统设计人员可以再一次进行选择上文所述的那个使用硅的多电平转换器架构,也可以选择更简单的双电平或三电平 SiC模块解决方案。设计人员也可以用 SiC来提高工作电压,从而降低上游的发电和配电成本。然而,设计人员需要充分利用电机设计和技术进行开发,以充分利用 SiC的功能。但是直到今天,人们才认识到 SiC通过降低电流纹波来提高电机工作效率,以及通过降低损耗来提高逆变器效率的优势。在某些应用中,使用 SiC就可以使用尺寸更小得多的较高转速电机,并可能不使用齿轮箱。

上述所有系统都需要为系统控制电子器件(+/- 5V、12V、24V)以及较小的辅助照明和冷却系统提供低压电源。具有高压功能的较小额定电流模块可以帮助简化利用可用的交流中压为此供电的任务。这是超共源共栅概念的绝佳应用领域,因为其能够轻松按比例增加开关的电压。人们还可以利用与低压常关 MOSFET串联的 SiC JFET的常开特性来简化启动电路,这在低功率反激式转换器中已得到证明。根据功率电平,用户可以选择是使用电源模块,还是使用现成的 JFET组件创建基于电路板的组件。

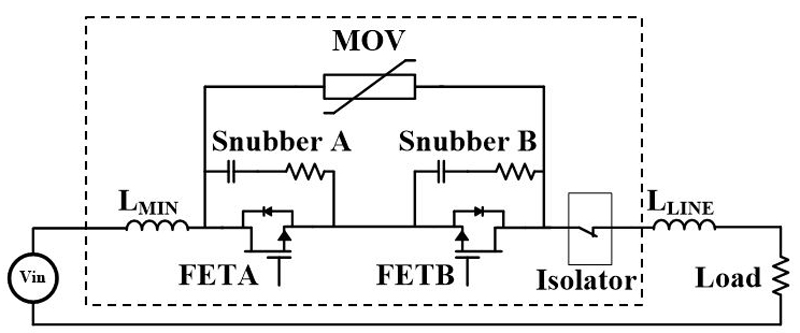

随着基于直流的发电和直流负荷的激增,人们将新的注意力集中在如何使用固态断路器来代替机械式断路器上,以提高可靠性、缩小尺寸、减少弧光问题并为系统保护加入智能。由于固态断路器没有活动部件,并且不会试图以机械方式断开电流,因此不会出现弧光问题或触点的机械磨损。固态方法在不强迫谐振零电流交叉的情况下中断直流电流的主要价值在于,它可以轻松地在 1us内完成。随后,可以在零电流下断开一个更小的隔离开关,以提供电流隔离。这种方法大幅度减少了下游电路和电源必须处理的故障电流的持续时间和幅度。

图 8展示了通常与具有双向功能的固态断路器一起使用的布置类型的示例。由于电缆布线和负荷电感在大型电源系统中可能会有很大差异,因此,在中断直流故障电流时,必须消散线路电感中存储的能量。该能量可能非常大,因此被图 8中并联使用的金属氧化物压敏电阻 (MOV)吸收。缓冲元件在关闭期间调节单位时间内电压的变化 (dV/dt)和单位时间内电流的变化 (di/dt)。

图 8:双向固态直流断路器的实现。背对背开关在任一方向上提供隔离电压。电阻器-电容器 (RC)缓冲器可缓和开关电压转换。MOV大小适当,可吸收线路电感中最坏情况下存储的能量。使用超共源共栅开关,几乎可以实现任何电压或电流处理水平

此应用对于开关的主要要求是低导电损耗、容易实现电压和电流缩放,以及在大故障电流关闭条件下的稳健运行。超共源共栅方法在这里再次变得有益。SiC JFET具有很好的导通电阻正温度系数,阈值电压 (VTH) 与温度的比值几乎为平线,因此非常容易并联,从而使大电流缩放非常简单。借助超共源共栅技术,仅需驱动一个以公共电源为参考的低压 MOSFET来控制断路器的操作,即可轻松实现电压缩放。

如图 9所示,将超共源共栅与简单的运算放大器电路以及低压 MOSFET一起使用,可以实现插入损耗非常低的快速动作电流断路器,同时还可以最大程度地降低峰值故障电流。人们可以修改此类电路以管理浪涌电流,并且仅在发生实际故障时才跳闸。在此示例中,电压缩放由串联连接的器件完成,而电流缩放由并联级完成。

图 9:6500V、1000A限流断路器的设计示例。由并联的 8个并联串组成,每个串具有 5个串联的 JFET。跳闸电流能够正常的使用运算放大器上的参考电压进行设置。可以如图所示或通过使用低压 MOSFET的漏源导通电压 (VDS(ON))来检测电流

SiC器件是改善中高压应用领域中的电力电子器件的极佳候选方案。从固态变压器到兆瓦级电机驱动,从辅助电源系统到固态断路器,在这些应用中,我们已展示了一般的 SiC MOSFET,特别是基于 SiC JFET的超共源共栅如何提供非常引人注目的高性能和系统简化优势。这些应用的增长将推动未来基于 SiC的功率电子科技类产品的增长,且远超于21 世纪 20年代的电动车热潮。6