隔离式低压大电流输出DCDC变换器中几种副边整

发布时间:2024-06-23 作者: BB贝博艾弗森app下载

发布时间:2024-06-23 作者: BB贝博艾弗森app下载

随着计算机通信设施及新的网络商品市场需求的迅速增长,未来的电源市场是非常乐观的。市场对小功率变换器的需求更是呈现迅速上升趋势。据专家预测[1?2],在今后五年内,小功率DC/DC变换器的发展的新趋势是:适应超高频CPU芯片的迅速发展,DC/DC变换器将向低输出电压(最低可低到1.2V)、高输出电流、低成本、高频化(400~500kHz)、高功率密度、高可靠性(MTBF≥106h)、高效率的方向发展。

整流电路作为DC/DC变换器的重要组成部分,对整机性能的影响很大。传统的整流电路采取功率二极管,由于二极管的通态压降较高(典型值有0.4V~0.6V),因此整流损耗较大。而为满足各种数据处理集成电路对更快速、更低功耗和更高集成度的要求,集成芯片工作电压将逐步降低到1V~3V(现今的典型值为2.8V~3.3V)。在DC/DC变换器输出如此低的电压时,整流部分的功耗占输出功率的比重将更大,致使整机效率更低,成为电源小型化、模块化的障碍。应用同步整流技术,用低导通电阻MOSFET代替常规整流二极管,可以大幅度降低整流部分的功耗,提高变换器的性能,实现电源的高效率,高功率密度[3?4]。

考虑到DC/DC变换器副边整流电路的多样化,本文针对低压/大电流输出DC/DC变换器,对几种常用的副边整流电路做多元化的分析比较,对倍流整流拓扑进行了较详细的阐述,希望能对电源设计有所帮助。

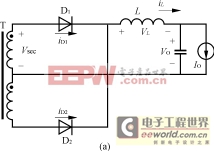

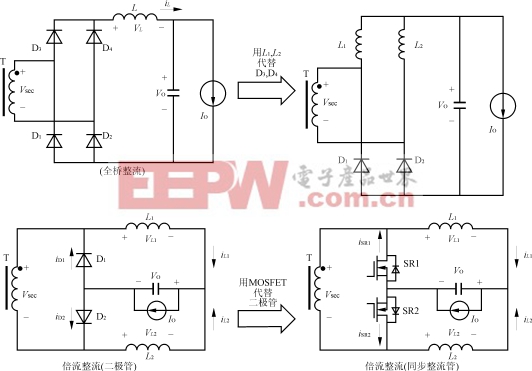

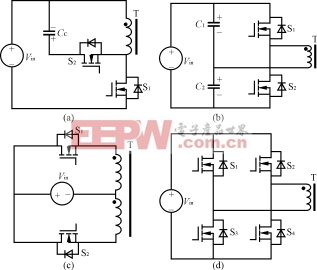

如图1、图2(a)、图3(a)、图4(a)所示,分别为全桥整流、半波整流、全波整流和倍流整流拓扑。全桥整流比其它三种整流方式多用两个整流管,使导通损耗大幅度提升,因而不太适合用于低压/大电流输出场合。故在下文中,未把全桥整流方式作为比较的对象。

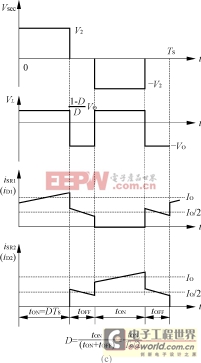

图2半波整流拓扑及其原理波形(a)二极管半波整流(b)MOSFET半波整流(SR)(c)原理波形

再作原理赘述,而着重对最近几年比较热门的“新型”整流拓扑—倍流整流方式来进行较详细的原理分析。

早在1919年,“倍流整流”思想[5]在汞弧管整流电路中就有人提出,但没有受到重视。随着最近几年低压/大电流输出DC/DC变换器的研究热潮,这种整流思想又重新得到了重视。它是从全桥整流方式演化而来,即用两只独立的,数值相同的电感代替全桥整流拓扑中的一组整流管,仍保持“全桥整流”的形式,经过适当变形,即得到图4所示的拓扑形式。图5给出全桥整流—倍流整流这一演化过程的示意简图。

如图4所示,VSEC是变压器副边绕组电压波形。下面对一个周期TS中,电路的工作情况做简要分析[6]。

(1)t0—t1:变压器副边绕组上为正压,SR2(D2)处于导通状态,SR1(D1)处于关断状态(SR1与D1,SR2与D2的开关状态分别对应一致,下文以SR管说明工作原理),电感L1上电流上升,L2上电流下降。对应如下关系式:

SR2都导通。通过电感L1、L2的电流都在减小,处于续流状态。对应关系式为:

处于导通状态,SR2处于关断态,电感L1上电流下降,L2上电流上升。对应关系式为:

(4)t3—t4:变压器副边绕组电压为零,整流管SR1、SR2都导通。通过电感L1、L2的电流都在减小,处于续流状态。对应电路方程与t1—t2时段相同。

在一个完整的开关周期Ts中,通过电感L1、L2的电流,都是在各自的0~DTs时间段内增加;在(1-D)Ts时间段内减小,且两段时间内电流增加量与减小量相等。对应如下关系式:

倍流整流,其实质就是两个电感的交错并联。电感L1与L2上的电压和流过电流相位相差180°,在变压器副边绕组电压非零时,流过L1、L2的电流一增一减,实现了iL1、iL2的纹波电流互消,从而使总的负载电流(i0=iL1+iL2)纹波大大减小。在输出电压纹波要求相同的情况下,这种倍流整流方式使得L1、L2显著减小,加快了功率级的动态响应。

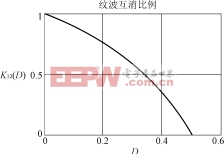

电感L1、L2电流波形相差180°,其合成电流(i0=iL1+iL2)纹波峰峰值与iL1、iL2纹波峰峰值的关系,用电流互消比例K12表示,K12与占空比D有关,关系式如下:

其对应的关系如图6所示。从图6可以直观地看出,当D=0.5,即V2=2V0时,才有完全的纹波互消作用(输出电流实现零纹波),D偏离0.5越远,纹波互消作用越差。当D=0.25时,纹波互消比例只有67%。因此,在倍流整流拓扑中,为了利用其纹波互消作用,希望D在0.5附近。

为了充分认识半波整流、全波整流和倍流整流拓扑的优缺点,便于优化选择,下面从整流管导通损耗,磁性元件尺寸,大电流绕组连接点数,SR驱动方式,原边适用拓扑等多个角度对三种整流方式逐一作比较。比较基于相同条件下进行,即变换器功率等级,开关频率fs,副边电压Vsec的幅值V2,各拓扑对应定义的占空比D,输出电压VO及其纹波ΔVO要求,输出滤波电容C相同。

(1)半波整流拓扑tON时段内,负载电流IO流过SR1;在tOFF时段内,IO流过SR2。因此在一个开关周期Ts中,两整流管总的导通损耗,相当于负载电流流经一个整流管的导通损耗(损耗计算公式用MOSFET)。基本关系式为:

式中:m为用作SR1或SR2的MOSFET的并联个数(SR1、SR2并联个数一般相等);

(2)中心抽头全波整流tON时段内,负载电流IO流过SR1或SR2;tOFF时段内,负载电流在两个整流管上平分,从而减小了tOFF时段内整流管的导通损耗,当用肖特基二极管作为整流管时,因肖特基伏安特性为指数关系,损耗降低量并不太明显。当采用MOSFET作为同步整流管,其电压电流近似呈线性关系,损耗降低得很明显,一个周期内整流管总的导通损耗近似为:

(3)倍流整流拓扑SR1、SR2中的电流流通情况与全波整流相似。一个周期内整流管总的导通损耗近似为:

三种整流方式整流管的导通损耗(基准值取为m·IO2Rds(on))与D的对应关系示于图7。由图7可知,D越小,全波整流和倍流整流拓扑中整流管的导通损耗与半波整流相比越小。从损耗角度考虑,当工作在Dmax(全波整流:Dmax=1;倍流整流:Dmax=0.5)附近时,后两种整流拓扑与半波整流相比,并无多大优势。

①半波整流拓扑电感上电压频率与开关频率fs相同,满足规定纹波要求的电感量[7]为:

的频率与开关频率fs相等,但由前面分析可知,拓扑中存在两个独立电感电流的纹波互消作用,而且两电感合成电流的频率为开关频率fs的两倍,在D靠近0.5时,纹波互消作用很显著,因而可以大幅度减小所需滤波电感值。满足规定纹波要求的电感量为:

可见,在相同条件下为满足相同的输出电压纹波要求,后两种整流拓扑所需的滤波电感值比前者显著减小,若半波整流输出滤波电感为参照值L,则采用全波整流只需·L,采用倍流整流只需·L,从而减轻了输出滤波电容器的纹波设计压力,减小了电感尺寸。当然这里给出的公式只能作为粗略的对比,并未考虑实际电容器的ESR和ESL的影响。

假定输出滤波电感很大,可忽略电感电流纹波,有iL=IO,iL1=iL2=IO/2。

①半波整流拓扑在SR1导通的tON时段内,负载电流IO流过变压器副边绕组,在SR2导通的tOFF时段内,变压器副边绕组电流为零。变压器副边电流有效值近似为:ISEC=IO·。

②中心抽头全波整流拓扑在SR1、SR2分别导通的tON时段内,负载电流IO分别流过变压器副边中心抽头绕组中的一只绕组;在SR1、SR2一起导通的tOFF时段内,负载电流在两只整流管上平分,中心抽头的两只绕组中,均流过一半的负载电流(IO/2)。变压器副边电流有效值近似为:ISEC=IO·(两个绕组均等于Isec)。

③倍流整流拓扑在SR1、SR2分别导通的tON时段内,一半的负载电流(假定IL1=IL2=IO/2)流过变压器副边绕组;在SR1、SR2一起导通的tOFF时段内,负载电流通过两个电感和两个整流管形成放电回路,并不流过变压器副边绕组(变压器绕组中只会流过很小的磁化电流,可忽略),也即在tOFF时段内,可以认为变压器副边绕组电流为零。副边电流有效值近似为:ISEC=IO·。

图8给出三种整流方式中变压器副边电流有效值(基准值为IO)与D的对应关系。可见,在D相等时,倍流整流与半波整流拓扑变压器副边绕组Irms相当。而这两个拓扑变压器副边绕组Irms与全波整流拓扑副边Irms的大小则与占空比D大小有关:当D0.33时,前者比后者小;D0.33时,前者比后者大。要注意的是中心抽头全波整流副边为两只绕组,而其它两种整流方式只有一只绕组。

特别需要指出的是,倍流整流拓扑这一电路形式特别适合于应用磁集成技术[8]。一般可采用两种集成思路:两只电感集成在一只磁芯上,以及两只电感与变压器集成在一只磁芯上。在倍流整流拓扑中,虽然由电感电流交错合成后的电流纹波较小,但分别流过分立电感L1、L2上的电流纹波却较大,因此在采用分立电感元件时,对应每只电感的磁通脉动量较大,引起较大的磁芯损耗,影响整机效率;把电感L1、L2集成在一只磁芯上(如EE或EI型),电感绕组分别绕制在两只外腿上,对应的磁通在中心柱上交叠,能轻松实现磁通脉动量的互消作用,从而大大减小中心柱的磁芯损耗和磁芯体积。对应的示意图如图9所示[9]。

更进一步,可把三个分立磁性元件集成在一只磁芯上[10],如图10所示,同时实现了磁芯和绕组的集成,从而大大减小了磁性元件所占的总体积,简化了布局及封装设计,与半波、全波整流相比,具有非常明显的优越性。

考虑到几种整流电路应用于大电流输出场合,因此对大电流绕组数和绕组连接点数进行了比较。

(2)全波整流拓扑有3只大电流绕组,5个大电流绕组连接点(假定中心抽头结构中,副边两只绕组的中间连接在绕组内部完成)。

(3)倍流整流拓扑有3只大电流绕组,6个大电流连接点;考虑两电感与变压器的集成后,只有2只大电流绕组,3个大电流绕组连接点。可见,应用磁集成技术后的倍流整流拓扑与前两个整流拓扑相比,大电流绕组数、大电流绕组连接点数都较少,因此副边的布局大大简化,与布局相关的损耗也得以逐步降低,使得整机封装设计变得容易。

——外加控制驱动(ExternalControl):通过附加的逻辑控制和驱动电路,产生出随主变压器副边电压作相应时序变化的驱动信号,驱动同步整流管。这种驱动方式的驱动信号电压幅值恒定,不随副边电压幅值变化,驱动波形好,但需要一套复杂的控制驱动电路,增加了成本,也延长了研发时间。

——自驱动同步整流(Self-drivenSynchronousRectification):即从电路中的某一点,直接获取电压驱动信号,驱动同步整流管,很常用的是从主变压器的绕组上直接获取驱动电压。这种驱动方案简单、经济、可靠,但驱动波形质量不如外加控制驱动电路理想[11]。

①半波整流拓扑如图2所示连接,可以直接从变压器副边获取电压,驱动SR工作,这在5V及3.3V等标准电压输出的DC/DC变换器中,已得到广泛的应用。在输出电压更低时,可在主变压器上加绕辅助绕组,获得幅值足够驱动同步整流管的驱动电压。

②全波整流拓扑与倍流整流拓扑因为主变压器副边电压存在较长的为零时段(tOFF),如果采用直接从变压器副边获取电压的自驱动SR方法,在这些tOFF时段,SR1、SR2均关断,电感电流将流过SR1、SR2的体二极管,致使整流部分的功耗增大,失去采用同步整流管的优势。相关文献[6]提出一种混合驱动方式,采用对称半桥倍流整流拓扑,利用电路的寄生参数,使得tOFF时段内SR1、SR2都能导通,虽然不失为一种思路,但没办法保证在所有的负载范围内,对应tOFF时段SR1、SR2都能有效开通,而且SR1、SR2的正确开关工作受变压器漏感的影响很大,而在变压器制造中,很难保证漏感的一致性,因此实用价值并不明显。对于这种副边电压存在比较大tOFF时段的拓扑,较多的采用外加控制驱动,保证了开关时序的准确性,从而确保了电路工作的可靠性及性能。

①半波整流拓扑原边拓扑较多的采用正激电路,因而选择何种磁复位方法最重要,它将决定主变压器的工作方式[12]。区别于其它磁复位方法,采用图11(a)所示的有源钳位正激电路可使主变压器双向磁化,从而减小主变压器的体积。

②全波整流拓扑通常与图11(b)、(c)、(d)对隔离式低压/大电流输出DC/DC变换器中几种副边整流电路的比较备注:m:作为同步整流管使用的MOSFET并联数目;Rds(on):MOSFET导通电阻;

*:根据不同的复位方法,有些拓扑可以工作在D0.5,但一般折衷优化考虑D0.5;

***:假定全波整流拓扑中,两个副边绕组的中间连接在绕组内部完成,括号内的数为采用磁集成技术后的数量;

③倍流整流拓扑文献[13]给出正激拓扑与倍流整流拓扑结合使用的拓扑形式—正-反激电路,这种电路在原边主管关断,辅管处于通态时,变压器作为能量源,磁化电流高达IO/2反映到原边值(IO代表负载电流),增加了原边开关的电流应力和损耗,变压器设计也相对复杂。基于以上考虑,本篇未对这一拓扑作对比选择。

在低压/大电流输出场合,推挽、对称半桥、全桥这些对称的原边拓扑,更适合与倍流整流拓扑结合使用。

在这三种拓扑中,同等条件下,全桥原边功率管的电流应力和电压应力最低;半桥拓扑原边功率管的电流应力是全桥的两倍,电压应力与全桥相等;推挽拓扑原边功率管的电压应力是全桥的两倍(推挽常因存在漏感问题,使得实际电压应力高于两倍输入电压),电流应力与全桥相等。所以能推知:今后低压/大电流输出DC/DC变换器,对于12V和48V的推荐总线电压,推挽拓扑更适合于12V总线V总线输入;全桥拓扑兼有功率管电流应力低和电压应力低的优点,但全桥拓扑器件数量相对较多,因而从器件数和整体的简单性这一方面出发,全桥并非最好的选择。但随着高频化的发展的新趋势,为提高变换效率,必然要求实现原边功率管的软开关,而全桥移相PWMDC/DC变换器则很容易实现主管ZVS的要求,因此在高频、低压/大电流输出DC/DC变换器中,全桥拓扑仍不失为较好的选择。

以上对三种整流电路进行了详细的比较,这里把相关联的内容作一小结,如表1所列。

本文针对隔离式低压/大电流输出DC/DC变换器的应用场合,对副边半波整流、全波整流、倍流整流三种整流方式来进行了详尽的分析比较,指出各自的优缺点和应用指导,并得出结论:结合磁集成技术和同步整流技术的倍流整流拓扑,非常适合于隔离式低